TSMC برای حافظه HBM4 روی گرههای 12 و 5 نانومتری خود پایه میسازد.

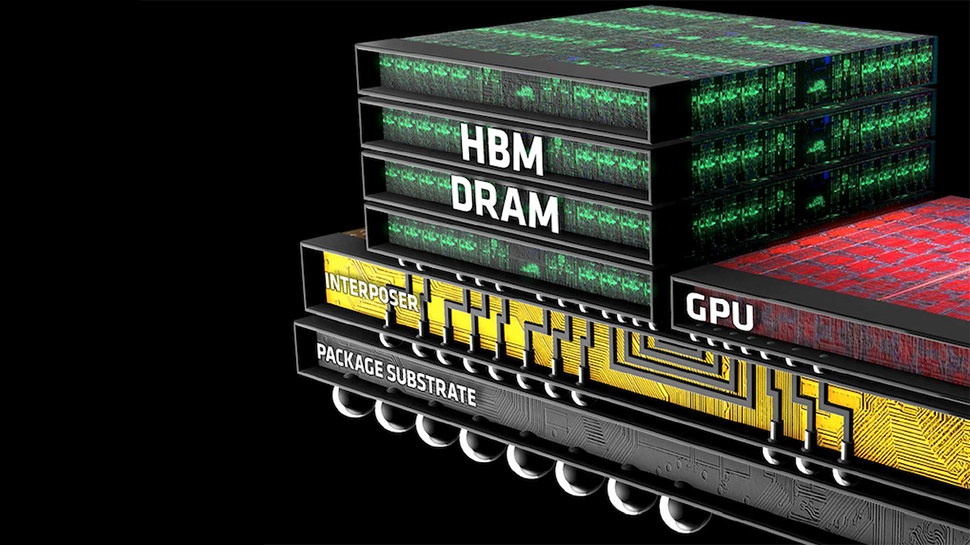

در اوایل سال جاری، SK hynix و TSMC همکاری خود را برای توسعه و ساخت پایه حافظههای HBM4 اعلام کردند، اما از افشای جزئیات رسمی خودداری کردند. به گزارش AnandTech، در سمپوزیوم فناوری اروپا 2024 این هفته، TSMC گفت که با استفاده از فناوریهای فرآیند 12FFC+ (کلاس 12 نانومتر) و N5 (کلاس 5 نانومتر) قالبهای پایه HBM4 را میسازد. استفاده از چنین گره های پیشرفته ای HBM4 را قادر می سازد تا عملکرد بی سابقه و بهره وری انرژی را ارائه دهد.

مدیر ارشد پلتفرم طراحی و فناوری در TSMC گفت: «ما با شرکای کلیدی حافظه HBM (میکرون، سامسونگ، SK hynix) بر روی گرههای پیشرفته برای ادغام کامل پشته HBM4 کار میکنیم. دای پایه مقرون به صرفه 12FFC می تواند برای عملکرد به HBM برسد و قالب پایه N5 می تواند منطق بیشتری را با قدرت بسیار کمتر در سرعت های HBM4 ارائه دهد.

فناوری فرآیند N5 TSMC در حال حاضر یکی از پیشرفته ترین گره های تولید موجود است. از آن برای ساخت برخی از بهترین CPU ها و بهترین GPU ها استفاده می شود، بنابراین استفاده از آن برای حافظه کار بزرگی است. چیزی که چنین گره پیشرفته ای اجازه می دهد این است که منطق و ویژگی های بیشتری را در قالب پایه HBM4 قرار دهد و همچنین گام های اتصال بسیار خوب را فعال کند (ما در مورد گام های 9 تا 6 میکرون صحبت می کنیم)، که برای اتصال مستقیم بر روی تراشه های منطقی ضروری هستند. افزایش عملکرد حافظه برای پردازنده های AI و HPC.

پایه های ساخته شده بر روی فرآیند 12FFC+ TSMC (برگرفته از فناوری 16 نانومتری FinFET تاسیس شده این شرکت) امکان ساخت پشته های حافظه 12-Hi و 16-Hi HBM4 را فراهم می کند که به ترتیب ظرفیت های 48 و 64 گیگابایتی را ارائه می دهند. استفاده از 12FFC+ دای های پایه “مقرون به صرفه” را فعال می کند که از اینترپوزرهای سیلیکونی برای اتصال حافظه به پردازنده های میزبان استفاده می کنند.

گره های تولیدی TSMC برای قالب های پایه HBM4

| خالی | N12FFC+ | N5 |

| حوزه | 1X | 0.39X |

| منطق گیگاهرتز @ قدرت | 1X | 1.55 برابر |

| قدرت @ گیگاهرتز | 1X | 0.35X |

TSMC همچنین در حال بهینه سازی فناوری های بسته بندی خود، به ویژه CoWoS-L و CoWoS-R، برای پشتیبانی از ادغام HBM4 است. این روشهای بستهبندی پیشرفته، ساخت اینترپوزرهای تا هشت اندازه شبکه را امکانپذیر میسازد و مونتاژ حداکثر ۱۲ پشته حافظه HBM4 را تسهیل میکند. اینترپوزرهای جدید دارای حداکثر هشت لایه خواهند بود تا از مسیریابی کارآمد بیش از 2000 اتصال داخلی و در عین حال حفظ یکپارچگی سیگنال مناسب اطمینان حاصل کنند. طبق یک اسلاید TSMC، تا کنون، پشته های حافظه تجربی HBM4 به سرعت انتقال داده 6 GT/s در 14 میلی آمپر رسیده اند.

نماینده TSMC گفت: “ما همچنین CoWoS-L و CoWoS-R را برای HBM4 بهینه می کنیم.” “هر دو CoWoS-L و CoWoS-R [use] بیش از هشت لایه برای فعال کردن مسیریابی HBM4 از بیش از 2000 اتصال داخلی با [proper] یکپارچگی سیگنال ما با شرکای EDA مانند Cadence، Synopsys و Ansys همکاری می کنیم تا یکپارچگی سیگنال کانال HBM4، IR/EM، و دقت حرارتی را تایید کنیم.”

تلاشهای مشترک TSMC با تولیدکنندگان برجسته حافظه مانند Micron، Samsung، و SK hynix، و همچنین شرکای EDA از جمله Cadence، Synopsys و Ansys، برای فعال کردن زیرسیستمهای حافظه HBM4 در چند سال آینده بسیار مهم است.

تلویزیون

تلویزیون

کیس گیمینگ و طراحی و مهندسی

کیس گیمینگ و طراحی و مهندسی کیس خانگی/اداری/دانشجویی

کیس خانگی/اداری/دانشجویی مینی کیس

مینی کیس کامپیوتر سرور و ورک استیشن

کامپیوتر سرور و ورک استیشن All In One

All In One

مادربورد سوکت LGA1851

مادربورد سوکت LGA1851 مادربوردهای DDR4 و DDR5**

مادربوردهای DDR4 و DDR5** مادربوردهای LGA 1700 **

مادربوردهای LGA 1700 ** سوکت LGA 1150

سوکت LGA 1150 سوکت LGA 1155

سوکت LGA 1155 سوکت LGA 1151 نسل 6 و 7

سوکت LGA 1151 نسل 6 و 7 سوکت LGA 1200

سوکت LGA 1200 سوکت LGA1151 نسل 8 و 9

سوکت LGA1151 نسل 8 و 9 سوکت LGA 1700 DDR4

سوکت LGA 1700 DDR4 سوکت LGA 1700 DDR5

سوکت LGA 1700 DDR5

هارد SSD فضای ذخیره سازی SSD

هارد SSD فضای ذخیره سازی SSD هارد اکسترنال

هارد اکسترنال هارد دسکتاپی

هارد دسکتاپی هارد لپتاپی

هارد لپتاپی