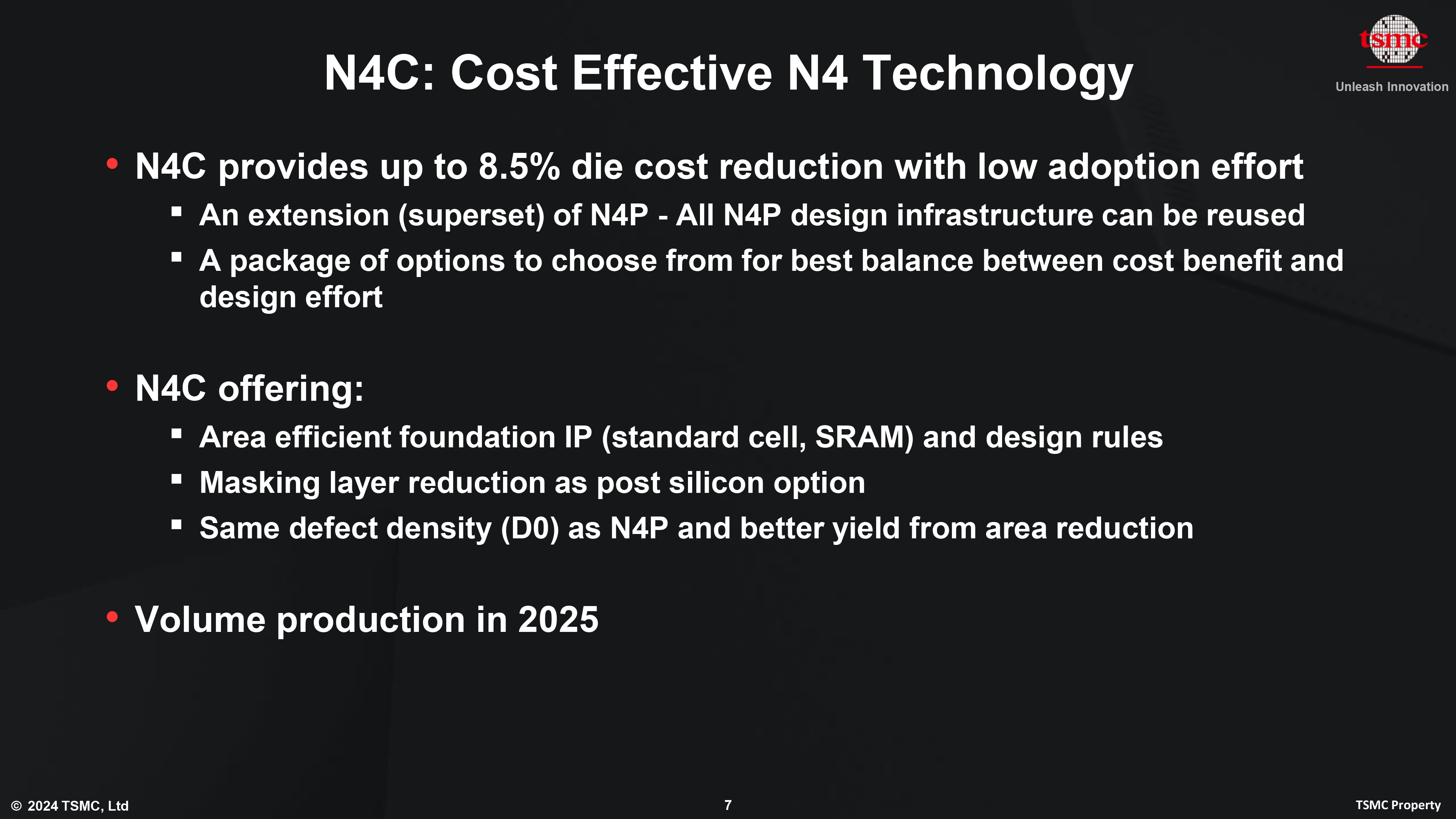

TSMC از فناوری جدید تولید کلاس 4 نانومتری خود، N4C، در سمپوزیوم فناوری آمریکای شمالی 2024 پرده برداری کرده است. این فرآیند ساخت جدید قرار است با ارائه کاهش قابل توجه هزینه و بهینه سازی کارایی طراحی، گره های تولید کلاس 5 نانومتری این شرکت را بهبود بخشد.

“بنابراین، ما کار 5 نانومتری و 4 نانومتری خود را تمام نکرده ایم [technologies]کوین ژانگ، معاون توسعه کسب و کار در TSMC گفت: “از N5 تا N4، ما به 4% کاهش چگالی انقباض نوری دست یافته ایم و به بهبود عملکرد ترانزیستور ادامه می دهیم. اکنون N4C را به مجموعه فناوری 4 نانومتری خود وارد می کنیم. N4C به مشتریان ما این امکان را می دهد که هزینه های خود را با برداشتن برخی از ماسک ها کاهش دهند و همچنین طراحی IP اصلی مانند سلول استاندارد و SRAM را بهبود بخشند تا هزینه مالکیت در سطح کلی محصول را کاهش دهند.

فناوری فرآیند N4C بخشی از خانواده گره های N5/N4 TSMC است و بر اساس فناوری N4P ساخته شده است. با طراحی مجدد سلول استاندارد و سلول SRAM، تغییر برخی قوانین طراحی و کاهش تعداد لایههای پوشاننده استفاده شده، TSMC قصد دارد هزینهها را تا 8.5 درصد کاهش دهد. این تغییرات نه تنها فرآیند تولید را ساده میکند، بلکه اندازه قالبها را نیز کاهش میدهد، که به طور بالقوه میتواند عملکرد را به دلیل پیچیدگی کمتر و نیاز به مساحت کوچکتر بهبود بخشد.

این گره مقرون به صرفه از زیرساخت طراحی مشابه N4P استفاده می کند، اگرچه هنوز مشخص نیست که آیا IP از N5، N4 و N4P می تواند مستقیماً به تراشه های مبتنی بر N4C منتقل شود یا خیر. این باعث ایجاد برخی عدم اطمینان در مورد سازگاری با طرح های موجود می شود. ما هنوز نمی دانیم که انتقال آن به N4C از N5 یا N4 چقدر آسان خواهد بود. TSMC نشان میدهد که بهترین تعادل را بین سود هزینه و تلاش طراحی ارائه میکند، تا بتواند فرآیند N4C خود را تشویق کند، اما جزئیات هنوز مشخص است.

معرفی N4C از نظر استراتژیک برای TSMC مهم است زیرا راهی را برای مشتریان فراهم می کند تا هزینه های تولید خود را برای یک گره کلاس 4 نانومتری به میزان قابل توجهی کاهش دهند، که ممکن است باعث پذیرش این فناوری فرآیند در بین مشتریانی شود که به دنبال هزینه های نسبتا پایین هستند. گره جدید ترکیب مناسبی از قدرت، عملکرد و مساحت (PPA) را نوید می دهد که آن را به گزینه ای جذاب برای بسیاری از مشتریان TSMC تبدیل می کند.

با توجه به هزینههای بالای مرتبط با فناوریهای کلاس 3 نانومتری و مزایای نسبتاً محدود آنها نسبت به گرههایی مانند N4P از نظر عملکرد و تراکم ترانزیستور، N4C یک انتخاب محبوب است.

TSMC انتظار دارد در سال 2025 تولید تراشههایی را با استفاده از فناوری N4C آغاز کند. با شش سال تجربه در فرآیندهای ساخت کلاس 5 نانومتری تا آن زمان، این شرکت پیشبینی میکند که N4C به بازدهی خوب و حفظ هزینههای پایینتر دست خواهد یافت و جذابیت آن را به عنوان یک مقرونبهصرفه تقویت میکند. راه حل تولید در صنعت نیمه هادی. در واقع، تا سال 2025، بسیاری از ابزارهای fab در فابهای با قابلیت 5 نانومتر مستهلک خواهند شد، بنابراین N4C و گرههای مشابه ممکن است در واقع مقرون به صرفه باشند.